私はRP1のドキュメントを読んだ。

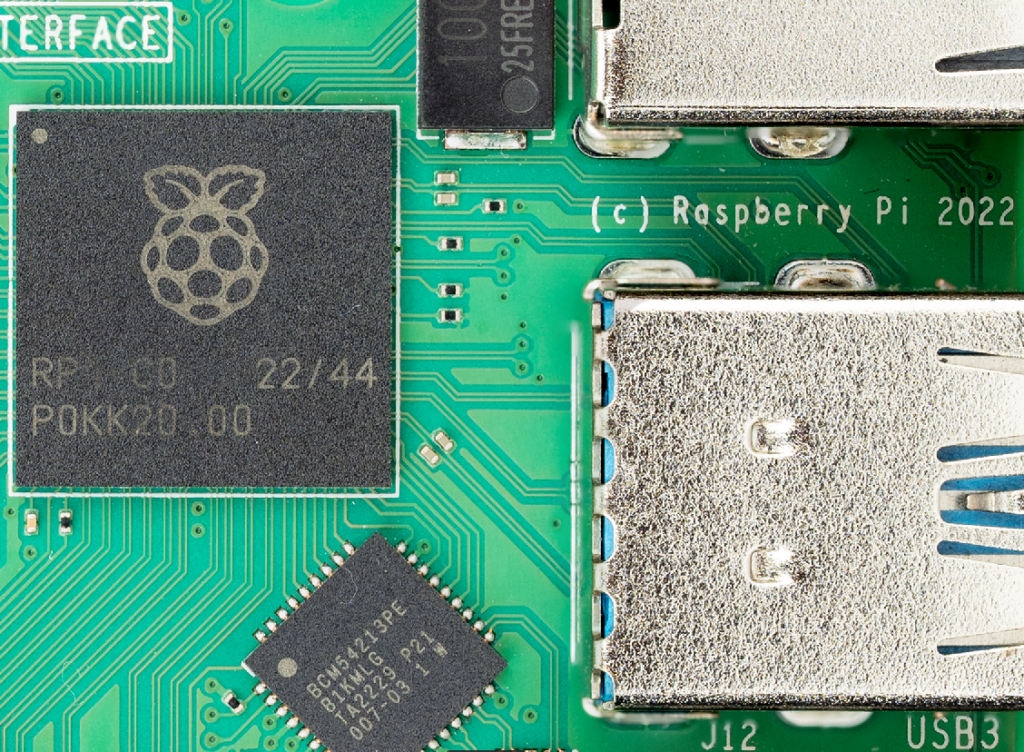

新しいRaspberry Pi 5の最も注目すべき特徴の1つは、Raspberry Piのフラッグシップ製品に初めて自社設計のシリコンチップであるRP1が搭載されたことです。この記事では、RP1の要点を説明し、何が革命的なのかをお伝えしたい。

残念ながら、この記事は "RP1のすべて "に相当するものではない。

その代わりに、彼らは 90ページのドラフト・データシート RP1の基本的な部分を説明する。

では、RP1の歴史から始めよう。

歴史

つまりRP1は、ラズベリーパイで最も長く続いている社内シリコンプロジェクトなのだ。だから「RP」と呼ばれている。1“.

Raspberry Pi 5の発表の中で、Eben Uptonはこう書いている。"2016年から開発が進められているRP1は、Raspberry Piでこれまで取り組んできたプログラムの中で、最も長く、最も複雑で、($1500万という)最も高価なプログラムです。"

それは ロングラン, 最も複雑としています。 最も高い プログラムだ。

しかし、ラズベリーパイがリリースした最初の自社開発シリコンではない。RP2040はPicoとPico Wに搭載されているマイクロコントローラーだ。

ラズベリー・パイ社内では、誰もがRP1のことを「プロジェクトY」と呼んでいた。

では、RP1がどのようなものなのかを見ていこう。

特徴

以前のモデルでは、基本的にすべてのI/Oはメインプロセッサーに統合されていた。

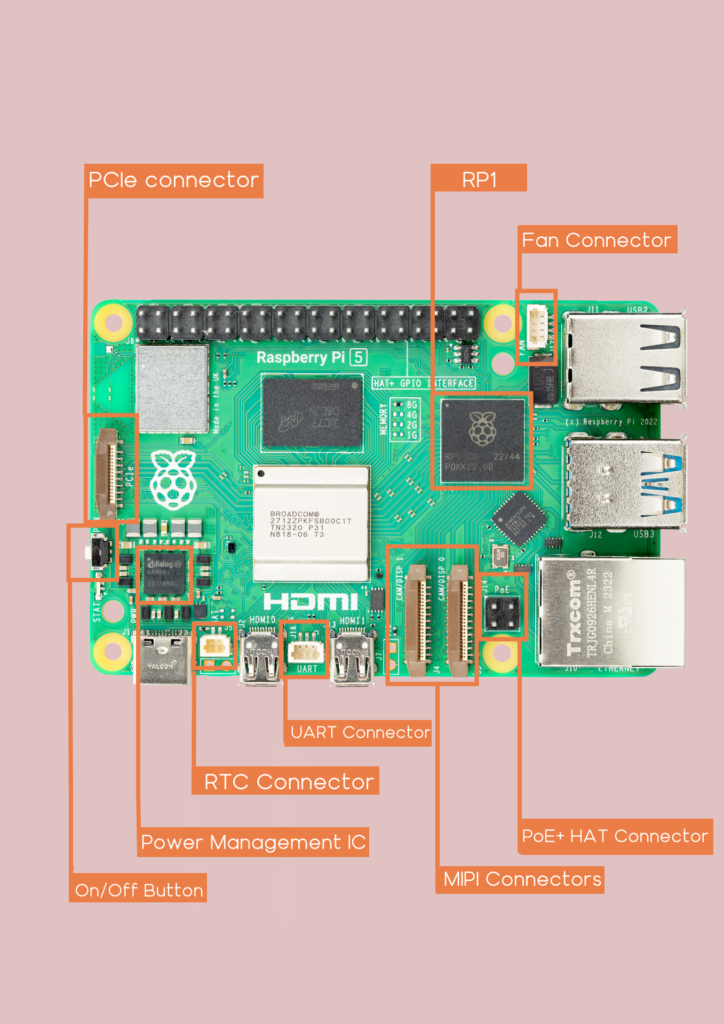

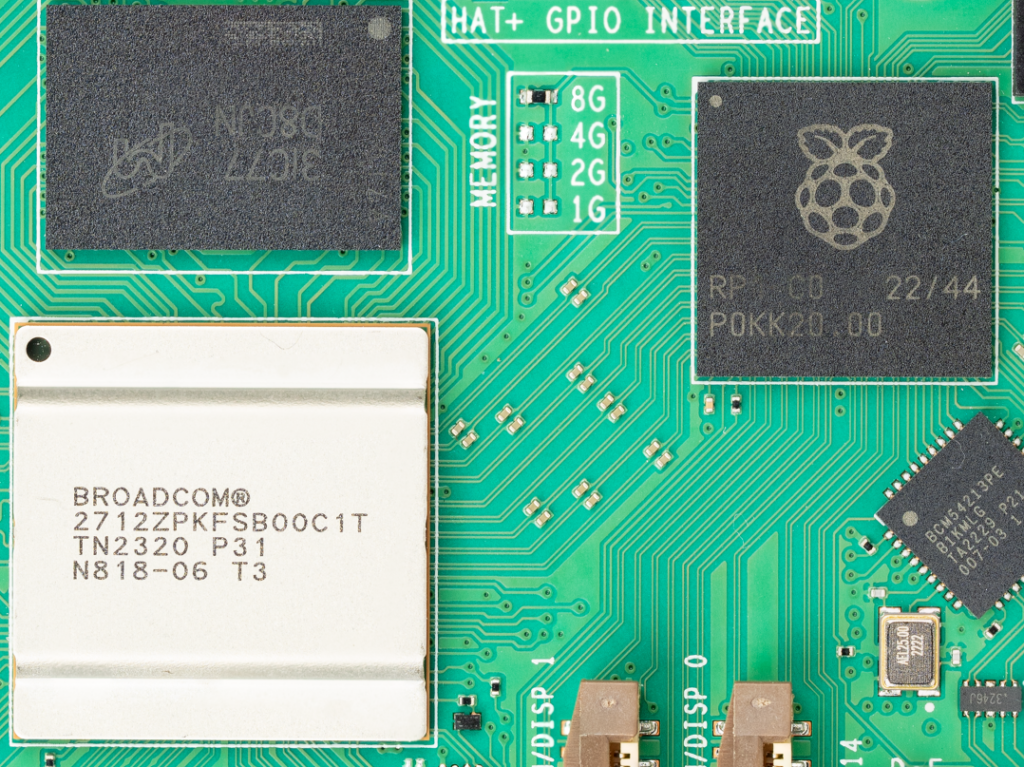

RP1の主なアイデアは、I/Oをメインプロセッサー(この場合はBroadcom BCM2712)から分離することだ。つまり、Raspberry Pi 5のI/O機能の大部分を担うサウスブリッジなのだ。

これにはさまざまな効果があり、そのひとつがメイン・プロセッサーの微細化である。すでに取り上げたように、BCM2712は16nmプロセス・ノードである。

一方、RP1自体は40nmプロセス・ノードである。

これにより、メインプロセッサーはより複雑なタスクに集中できる。

そのため、BCM2712は最も速いインターフェイスを引き継ぎ、遅いインターフェイスはRP1に残す。次のセクションで詳しく説明する。

しかし、RP1とBCM2712の2つのチップは連携し、4レーンのPCIe 2.0バスで接続される。これは高速な接続だが、両者の間に多少のレイテンシが発生するのは避けられない。

RP1の内部スペックに目を向けてみよう。

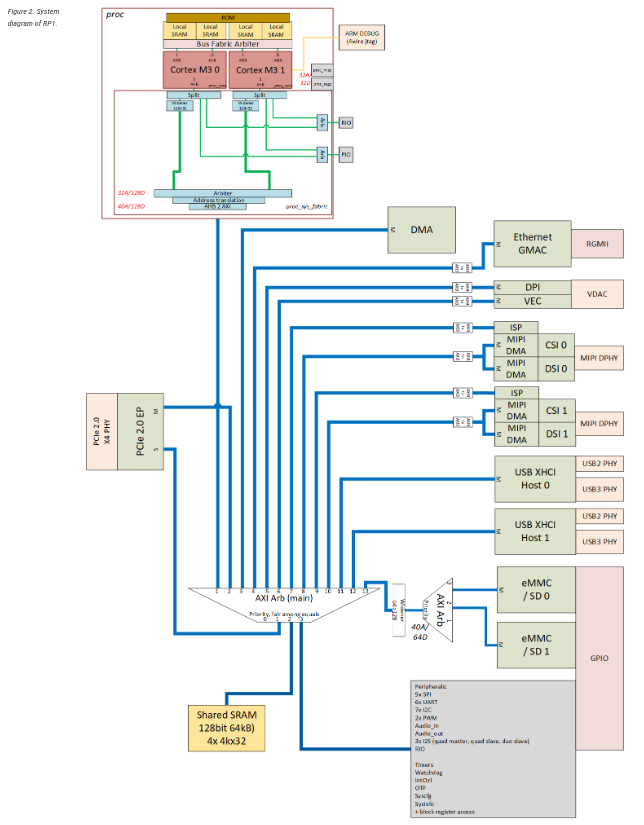

参考のためにRP1のダイアグラムの写真を下に載せておく。

つまり、RP1には、Arm Cortex-M3アーキテクチャに基づく2つのプロセッサ・コア(図左上の赤いボックス内のCortex M3 0とCortex M3 1)が搭載されている。

また、8チャンネルのDMAコントローラーを搭載しており、チップは最大8つの異なる周辺機器のデータ転送を同時に管理できる。

このチップには3つのPLLが内蔵されています:独立したビデオ・クロックとオーディオ・クロックを生成する2つのフラクショナルN PLLと、システム・クロックを生成する1つの整数PLLです。

RP1はまた、500kSPSで動作する12ビット分解能、5入力の逐次近似アナログ・デジタル(ADC)コンバータを備えており、4つの外部入力と1つの内部温度センサを備えています。

下図を見ると、左下に「Shared SRAM 128bit 64kB) 4x 4kx32」と書かれた黄色いボックスがあることに気づくだろう。これは、BCM2712とRP1の両方のバス・マスターからアクセス可能な64kBのメモリ部分があることを意味している。

このメモリーには4つのブロックがあり、各ブロックは4キロバイトで構成され、一度に32ビットのデータ転送ができる。

最後に、RP1 には DMA ペース用に設定できるタイムベース・ジェネレーターがある。タイムベース・ジェネレーターは、主にDMAのペーシングとGPIO入力イベントの安定化のために使用されます。

これがデータシートに掲載されているRP1の内部構造図である:

この写真では、RP1がどのように動作するのかが大体わかりますが、どの周辺機能を制御しているのかもわかります。

ペリフェラル・コントロール

右側には、下から順に以下のものが見える:GPIO、USB 3 PHY、USB 2 PHY、USB 3 PHY、USB 2 PHY、MIPI DPHY、MIPI DPHY、VDAC、RGMII。

そのため、RP1はGPIOピンと関連するペリフェラル・インターフェースを制御する:SPI、UART、i2C、PWM、i2S。デルタ・シグマPWMオーディオ出力も制御するが、ラズベリーパイ5にはオーディオジャックがないため、典型的なアナログ・オーディオは得られない。

また、USB 2.0およびUSB 3.0ポートも制御し、各ホスト・コントローラがダウンストリームのUSB 2.0およびUSB 3.0ポートを管理します。データシートによると、これは「すべてのダウンストリームポートが独立した無制限の帯域幅を持つ」ことを意味します。

リアム・フレイザーによれば、「PCIeリンクの帯域幅のおかげで、USB 3ポートを両方ともフル帯域幅で動作させることができるはずです」。これはRaspberry Pi 4からの大きなアップグレードだ!

RP1は、DSIとCSI-2をサポートする4レーンのMIPIトランシーバーを担当する。

PAL/NTSCとVGAをサポートする3チャンネルのビデオ・デジタル・アナログ・コンバーターを搭載している。

そして最後に、ギガビット・イーサネットMACを制御するのもRP1の責任だ。

この時点で、PIOについて気になっているかもしれない。残念なことに、RP1のすべてのドキュメントが公開されていないため、現時点ではわからない情報がたくさんある。

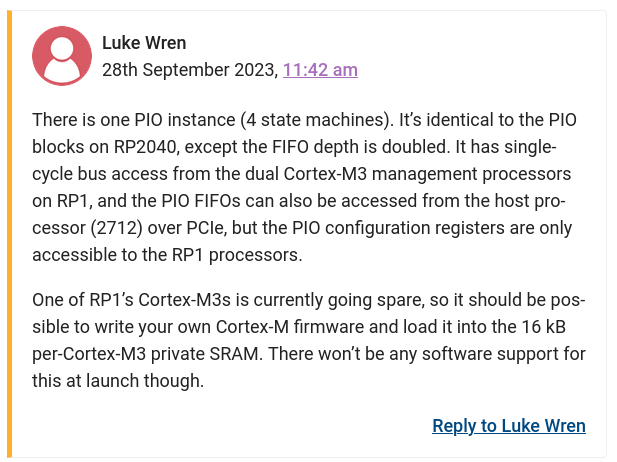

分かっているのは、RP1のPIOブロックはRP2040とは少し動作が異なるということだ。つまり、(RP2040のように)4つのステートマシンを持つ1つのPIOブロックがある一方で、FIFOの深さは2倍になっている。ルーク・レンのコメントをご覧ください:

つまり、現時点で分かっているのは周辺機器のコントロールだ。

時間が経てば、RP1に関するかなりの情報が発表されるに違いないからだ。

デメリット

RP1のクールな点についていくつか話してきたが、まったくバラ色のベッドというわけではない。

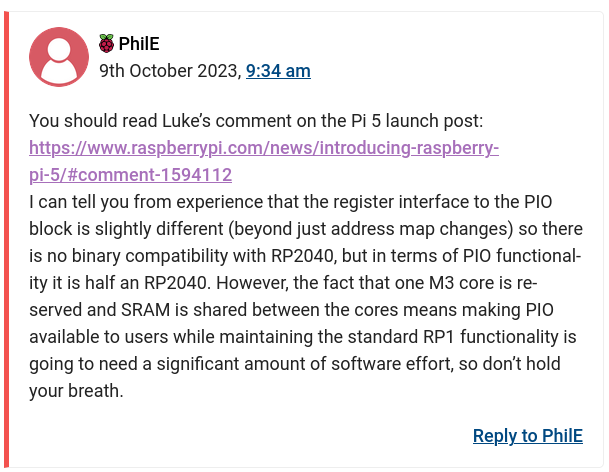

まず第一に、RP1のPIOはRP2040とは動作が異なります。フィルからのコメントをご覧ください:

I/OコントローラーをメインSoCから分離することのもう一つの欠点は、ある程度のレイテンシーが発生することだ。

データシートによれば、このレイテンシは「設計上のリンク幅と速度で通常1μs」であり、「ビットバッシュ・プロトコルなど、高速だがタイムリーな書き込みシーケンスに依存するアプリケーションや、ピンの状態変化に素早く反応する必要があるアプリケーション」にとっては問題となりうる。

未来はどうなるのか?

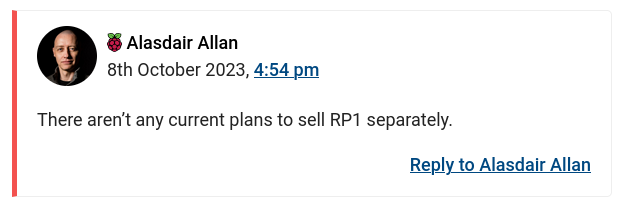

大きな疑問のひとつは、ラズベリーパイがRP1を単体で販売するかどうかだ。結局のところ、 RP2040は別売り.数日前のコメントで、Raspberry PiのAlasdair Allanは次のように答えていた:

もちろん、それは偏向である可能性もあるし、RP1を別に期待すべきではないという純粋な答えである可能性もある。この質問に関しては、時間が経ってみなければわからない。

RP1を別売りにしてくれたら最高だと思う。

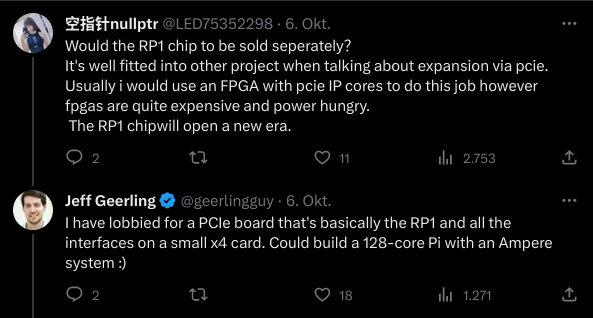

ジェフ・ギアリングが提案した最も興味深い選択肢のひとつだ:

もしかしたらラズベリーパイは、RP1チップとPCIeボードの両方を提供してくれるかもしれない!

様子を見るしかない。

コンテスト&ニュースレター

Raspberry Pi 5を10月23日まで待たなければならないことがどれほどもどかしいか、私たちは知っている。

だから、一刻も早く、皆さんに遊んでいただけるようにしたかったのです。

そこで、コンテストを設定した: Raspberry Pi 5で思いつく最もクレイジーなことは何ですか?

あなたのアイデアを送っていただければ、私たちのアイデアでそれを実現し、記事にします!

当選者の発表はこちらと buyzero.de 10月23日

採用されたアイデア(弊社が決定)には、27W USB-C Power Delivery(PD)電源、Raspberry Pi 5ケース、SDカード、Raspberry Pi 5を含むRaspberry Pi 5フルキットが当たります。EU圏内は送料無料です。

次点者にはRaspberry Pi 5(EU圏内送料無料)が贈られる。

詳細は以下のリンクから: ラズベリーパイ5が当たる!

結論

RP1の要点は以上だ。

冒頭で強調したように、この情報の一部は変更される可能性があります。Raspberry Piがより永続的なドキュメントをリリースしたら、必ず新しい記事を掲載します。

Raspberry Pi 5に関する他の記事もぜひご覧ください:

- ラズベリーパイ4とラズベリーパイ5の比較

- Raspberry Pi 5のファーストルック

- Raspberry Pi 5をクールに保つ

- Raspberry Pi 5でDOOM

- 無料でRaspberry Pi 5を当てよう

- Raspberry Pi 5の5つの驚くべき機能

- Raspberry Pi 5 マイクロSDカードの速度

- 4 Raspberry Pi 5に関するよくある質問

RP1を別売りにしてほしいですか?あるいは、ジェフ・ギアリングのようなPCIeボード?

下のコメントで教えてください!

主チップのすべてのE/Sペリフェリックを主プロセッサーから分離することは興味深い、

M3核を単独で持つためにRP1と分離してベンダリングすることを望まず、M4核とM7核で競争することを望んでいる。